### ANDANTE AI FOR NEW DEVICES AND TECHNOLOGIES AT THE EDGE

### Early Power Extraction with Cadence<sup>®</sup> Tools

Erfan Azarkhish

eaz@csem.ch

ANDANTE 1<sup>st</sup> WORKSHOP ON BENCHMARKING July 2<sup>nd</sup>, 2021

#### OUTLINE

- Overview of Power Extraction

- Challenges and Opportunities

- ${}^{\bullet}$  Early Power Extraction with Cadence Joules  ${}^{\mathbb{R}}$

- Results

2

Disclaimer: the following slides aim to provide an honest review of Cadence power extraction flows.

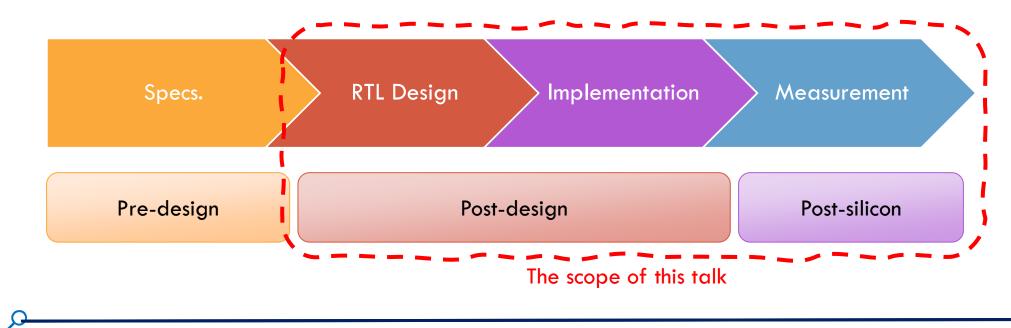

### **OVERVIEW OF POWER EXTRACTION**

- Estimation of **power consumption** before actual silicon measurement

- Challenges

- Accuracy compared with measurement

- Consistency across the design phase

### *TERMINOLOGY*

- VCD: Value Change Dump → Record activities chronologically

- TCF: Toggle Count Format

Probabilistic activity and toggle rate

- SDF: Standard Delay Format

5

# **POWER EXTRACTION APPROACHES**

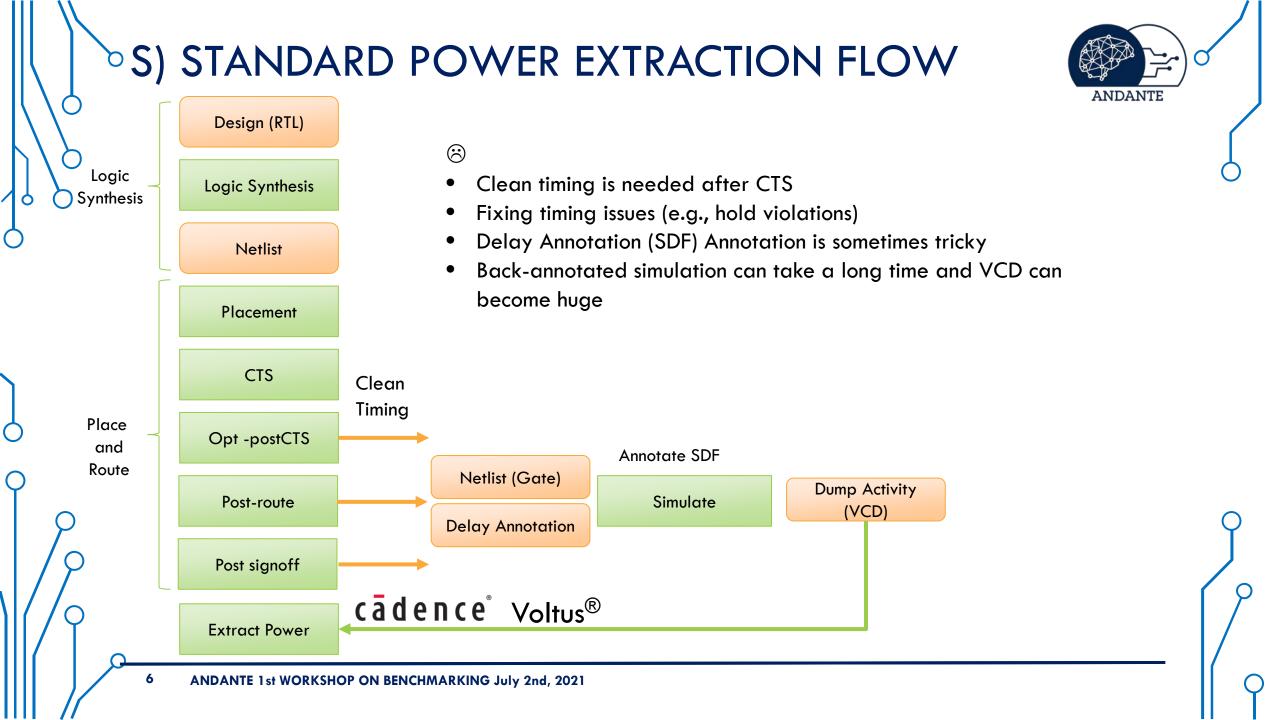

• S) Standard Power Extraction Flow

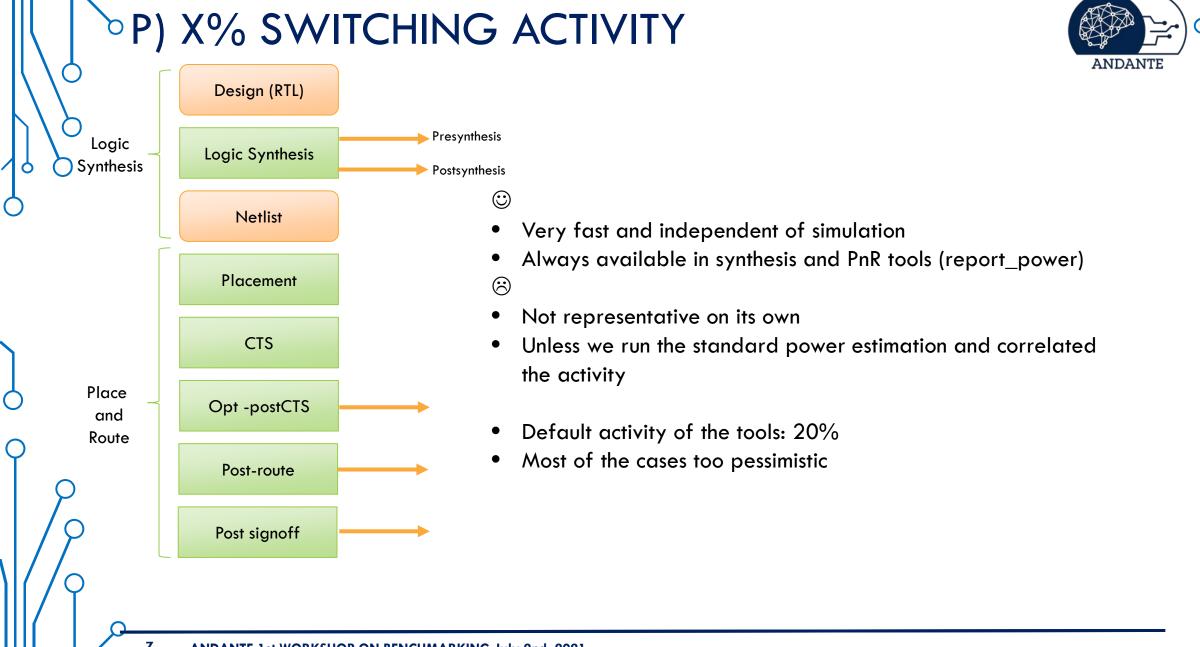

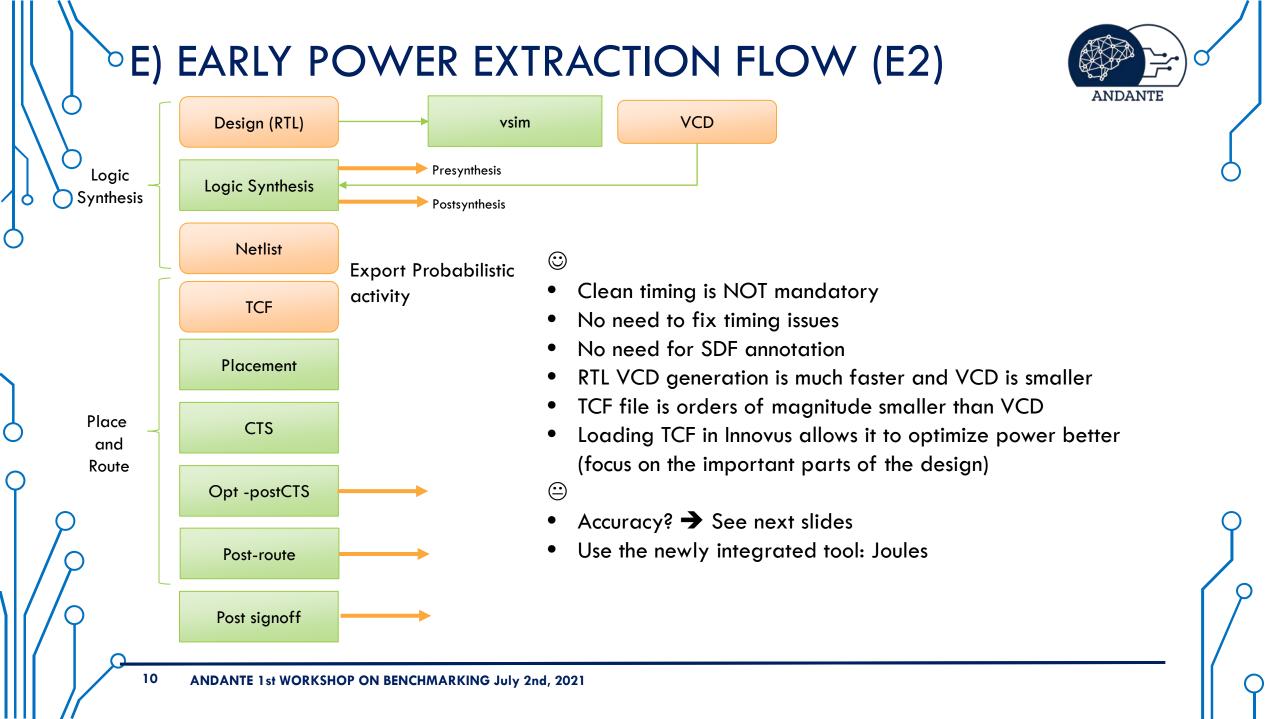

• P) Probabilistic Power Extraction (X% Switching Activity)

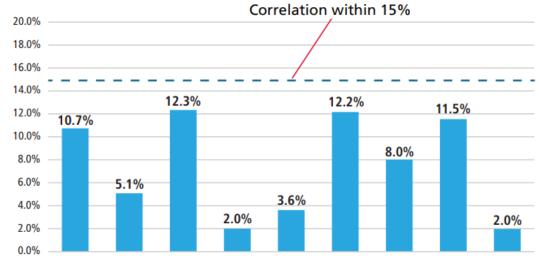

• E) Early Power Extraction Flow

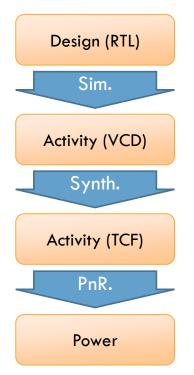

#### $\sim$ E) EARLY POWER EXTRACTION FLOW (E1) VCD Design (RTL) vsim Presynthesis Logic Synthesis Postsynthesis Clean timing is NOT mandatory No need to fix timing issues No need for SDF annotation RTL VCD generation is much faster and VCD is smaller $\bigcirc$ Accuracy? -> See next slides Use the newly integrated tool: Cadence Joules<sup>®</sup> cādence Joules RTL Power Solution Unified power calculator for accurate RTL power and signoff-quality gate power

https://www.cadence.com/en\_US/home/tools/digital-design-and-signoff/power-analysis/joules-rtl-power-solution.html

#### 0.0% implementation and signoff

• Direct integration with **Palladium** platform for quick peak power identification

## **©CADENCE JOULES® RTL POWER SOLUTION**

- Integrated within Genus<sup>®</sup> Synthesis Solutions

- Claims:

- RTL within 15% of signoff power

- Up to 20X faster time-based power analysis

- Bridge between verification,

Figure 1: Joules RTL Power Solution correlation to Voltus signoff power across real customer designs

#### **EXPERIMENTAL SETUP**

| Scenario | Application              | Design               | Node (nm) |

|----------|--------------------------|----------------------|-----------|

| А        | Coremark                 | RISC-V               | 22        |

| В        | Dhrystone                | RISC-V               | 22        |

| С        | Tree Traversal           | RISC-V + Accelerator | 22        |

| D        | Brain Signal Acquisition | ASIP                 | 180       |

Operating conditions are kept constant in each scenario

11

Ο

$\bigcap$

$\int c$

### **>ACTIVITY-BASED POWER EXTRACTION**

#### Design (RTL)

Pre-synthesis

0

Ó

Ò

$( \ )$

CTS

Opt – Post CTS

Routing

Opt - Post Route

Signoff

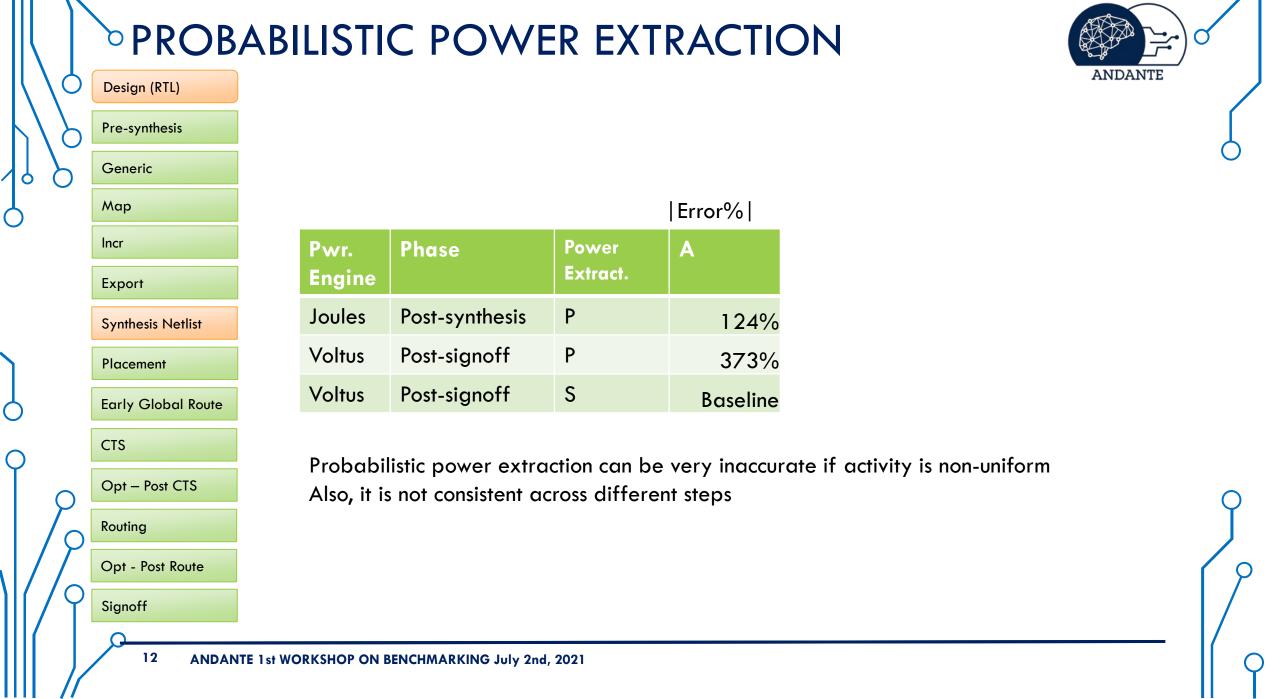

|                |                   |                   |     |       | Error% |     |

|----------------|-------------------|-------------------|-----|-------|--------|-----|

| Pwr.<br>Engine | Phase             | Power<br>Extract. | Α   | В     | C      | D   |

| Joules         | Pre-synthesis     | E1                | 29% | -     | -      | -   |

| Joules         | Post-synthesis    | E1                | 25% | 26%   | 28%    | 19% |

| Legacy*        | Post-synthesis    | E1                | 36% | -     | -      | -   |

| Voltus         | Post-place        | S                 | 16% | -     | -      | -   |

| Voltus         | Post-CTS hold opt | S                 | 5%  | -     | -      | -   |

| Voltus         | Post-route        | S                 | 3%  | -     | -      | _   |

| Voltus         | Post-signoff      | E2                | 12% | 15%   | 9%     | 7%  |

| Voltus         | Post-signoff      | S                 |     | Basel | ine    |     |

- : Not measured

#### ANDANTE 1st WORKSHOP ON BENCHMARKING July 2nd, 2021

13

C

### **>ACTIVITY-BASED POWER EXTRACTION**

#### Design (RTL)

Pre-synthesis

0

Ó

Ò

$( \ )$

CTS

Opt – Post CTS

Routing

Opt - Post Route

Signoff

|                |                   |                   |     |       | Error% |     |

|----------------|-------------------|-------------------|-----|-------|--------|-----|

| Pwr.<br>Engine | Phase             | Power<br>Extract. | A   | В     | C      | D   |

| Joules         | Pre-synthesis     | E1                | 29% | -     | -      | _   |

| Joules         | Post-synthesis    | E1                | 25% | 26%   | 28%    | 19% |

| Legacy*        | Post-synthesis    | E1                | 36% | -     | -      | -   |

| Voltus         | Post-place        | S                 | 16% | -     | -      | -   |

| Voltus         | Post-CTS hold opt | S                 | 5%  | -     | -      | -   |

| Voltus         | Post-route        | S                 | 3%  | -     | -      | -   |

| Voltus         | Post-signoff      | E2                | 12% | 15%   | 9%     | 7%  |

| Voltus         | Post-signoff      | S                 |     | Basel | ine    |     |

- : Not measured

#### ANDANTE 1st WORKSHOP ON BENCHMARKING July 2nd, 2021

#### **SILICON MEASUREMENT**

Ο

( )

$\bigcap$

Measurements match Standard Power Extraction within 5% of error

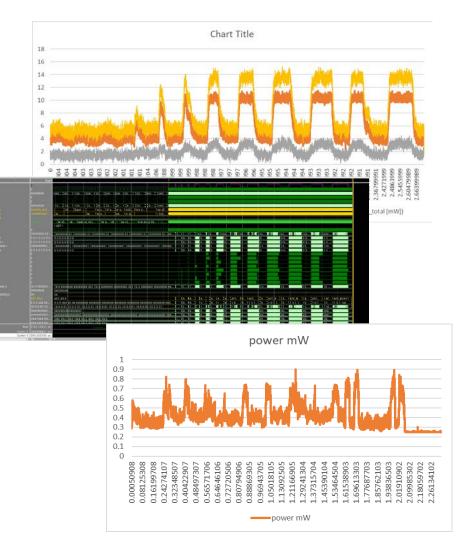

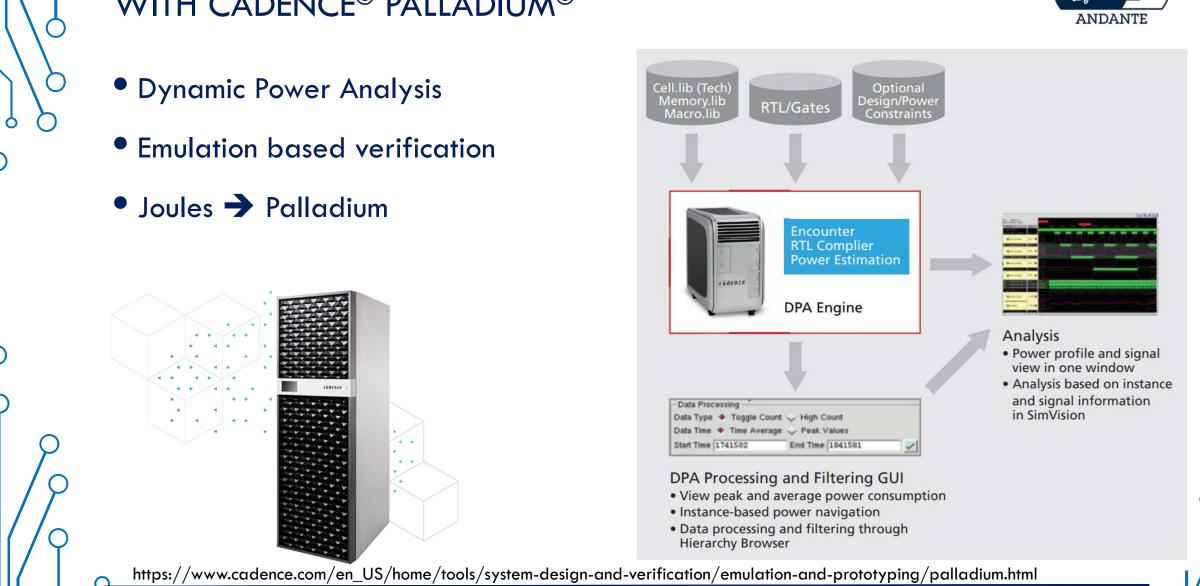

#### DYNAMIC POWER ANALYSIS (DPA) WITH CADENCE<sup>©</sup> PALLADIUM<sup>©</sup>

- S) Standard Power Extraction Flow

- The accurate and consistent approach

- P) Probabilistic Power Extraction (X% Switching Activity)

- Not reliable

- E1) Early Power Extraction Flow (error up to 30%)

- Faster but still accurate

17

Ċ

#### **SUMMARY**

- E2) Early Power Extraction Flow (error up to 15%)

- Trustable and accurate results

- Allow for activity-aware power optimization

- Consistent across the PnR flow

Ò

#### THANK YOU!

ANDANTE 1st WORKSHOP ON BENCHMARKING July 2nd, 2021