V Accelerators

**ANDANTE** Design and Implementation of Neuromorphic ASICs and Platforms for Edge Computing Application Solutions

### **Objectives**

- Design of neuromorphic accelerators (ANN and SNN) for edge computing solutions

- Validation of accelerators in dedicated platforms for various applications domains

- Evaluation of platforms and accelerators performances through realistic use cases

# **Hardware Challenges**

- Managing the complexity of different ASIC design

- technologies

- Integration of neuromorphic accelerators and sensors for various applications in the same platform Achieving high energy-efficiency

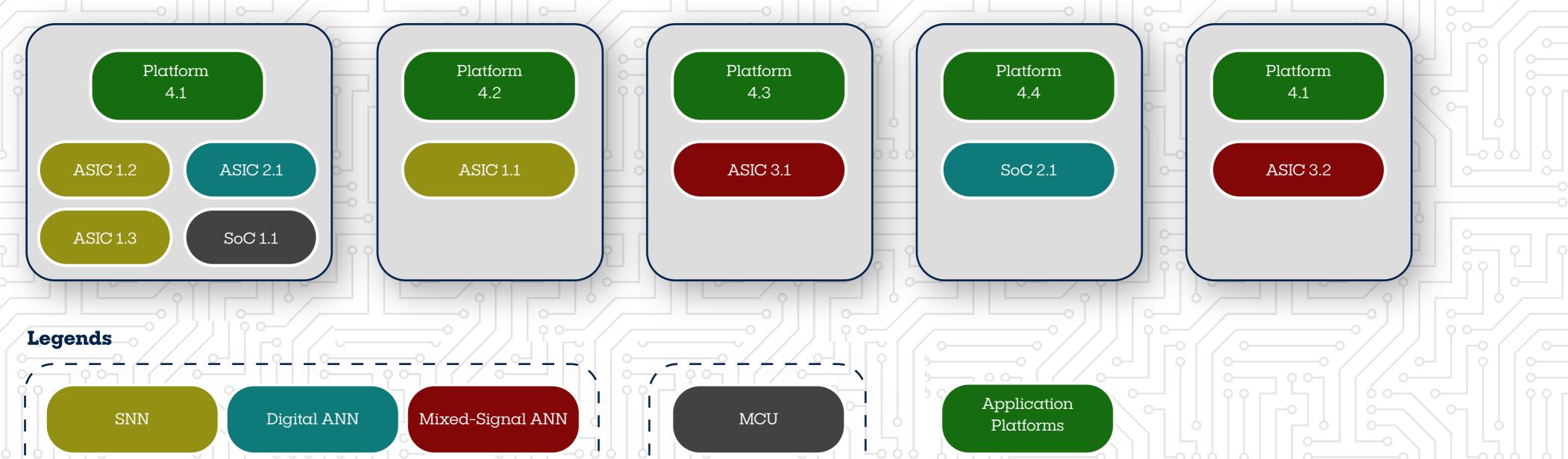

## **Main Components and Platforms for efficient Edge computing Solutions**

## Neuromorphic Accelerators for Edge Computing Solutions

|   | AI Components           | ANDANTE ID      | Description                                                                                                                                              | Technology             | Design Owner         |  |

|---|-------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------------|--|

|   | Mixed-signal SNN        | ASIC 1.1        | Multi-ASIC for exploration of parallelized and distributed SNN algorithms                                                                                | 28 nm CMOS             | Infineon             |  |

|   | Mixed-signal SNN        | ASIC 1.2        | Multi-core targeting low-dimensional signal representations, such as auditory signals, vibrations, or bio-signals not related to machine vision          | 28 nm FDSOI            | University of Zurich |  |

|   | Front-end               | <b>ASIC 1.3</b> | Audio front-end performing acoustic inference sensing tasks: acoustic feature extraction (AFE) and classification                                        | 40 nm                  | SynSense             |  |

|   | Digital <b>ANN</b>      | ASIC 2.1        | Feature extractor circuit to address image classification, segmentation and detection applications                                                       | 22nm FDX               | CEA                  |  |

| 0 | Digital <b>CNN</b>      | SoC 2.1         | Neural Compute Engine (NCE) targeting NN acceleration for smart vision applications in digital life domain                                               | 22nm FDX               | CSEM                 |  |

|   | Mixed-signal <b>ANN</b> | ASIC 3.1        | Inference accelerator with a multi-core architecture using analog in-memory computing; targeting voice activity detection (VAD)                          | 22nm FDX               | Fraunhofer           |  |

|   | Mixed-signal <b>ANN</b> | <b>ASIC 3.2</b> | Analogue neuronal network (aNN) for tinyML applications. To be evaluated in the context of one-key-word-spotting for a limited amount of accents         | 28nm CMOS<br>with RRAM | Infineon             |  |

|   | MCU                     | Soc 1.1         | Microcontroller STM32 aiming to identify best tradeoff between SoC features and functionality, having a direct impact on the silicon area and final cost | 28 nm or lower         | STMicroelectronics   |  |

Host

### **Evaluation Platforms for Various Edge Computing Applications**

| Platform/<br>board      | Short Descripti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | on                                                                                                                                                       | Associated<br>Components                                                                                                                        | Associated Domains and<br>Use Cases                                                                                                      | Contributors      |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|

| 4.1                     | STM32-based hybrid neuromorphic platform co<br>perform complementary and efficiently AI featu<br>Designed to support a variety applications in di<br>mobility, and digital life domains                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ires.                                                                                                                                                    | SoC 1.1,<br>ASIC 1.2,Digital Farming: UC2.1, UC2.2<br>Transport and Smart Mobility:<br>UC3.1, UC3.2, UC3.3, UC3.4<br>Digital life: UC5.1, UC5.2 | CEA,<br>STMicroelectronics,<br>SynSense, Televes,<br>University of Zurich                                                                |                   |  |

| 4.2                     | A Spiking Neural Microcontroller (SNMC) platfo<br>radar/optical sensor applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | orm intended, for instance, for                                                                                                                          | ASIC 1.1                                                                                                                                        | <b>Digital Industry:</b> UC1.1<br><b>Healthcare:</b> UC4.3                                                                               | Infineon          |  |

| 4.3                     | Includes a mixed-signal ASIC and controller/pe<br>instance for voice activity detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | eripheral units, suitable for                                                                                                                            | ASIC 3.1                                                                                                                                        | <b>Digital Industry:</b> UC1.1<br><b>Digital life:</b> UC5.1.4                                                                           | Fraunhofer        |  |

| 4.4                     | Provides effective interface between SynSense<br>camera with low latency and low power consu<br>human-computer interaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                          | SoC 2.1                                                                                                                                         | Digital life: UC5.2                                                                                                                      | CSEM,<br>SynSense |  |

| <b>ichie</b><br>ASIC an | An Analog Neuronal Network Microcontroller (An Analog Neuronal Net | ANMC) board; only intended for<br><b>Next Steps</b><br>Mid-term<br>• Detailed design<br>specifications<br>• Implementation of ASIC<br>SoCs and platforms | Long<br>• Val<br>plat                                                                                                                           | ASIC 3.2 Digital life: UC 5.1.5 Inf<br>Long-term<br>• Validation of hardware (ASICs,<br>platforms)<br>• Integration of tools and softwar |                   |  |

|                         | ations based on use case needs<br>vel design specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                          | bs,<br>• Delivery of hardware platforms to WP5<br>use cases implementation                                                                      |                                                                                                                                          |                   |  |